[Author Prev][Author Next][Thread Prev][Thread Next][Author Index][Thread Index]

gEDA-user: PCB Bug: poly clearance around rotated pads.

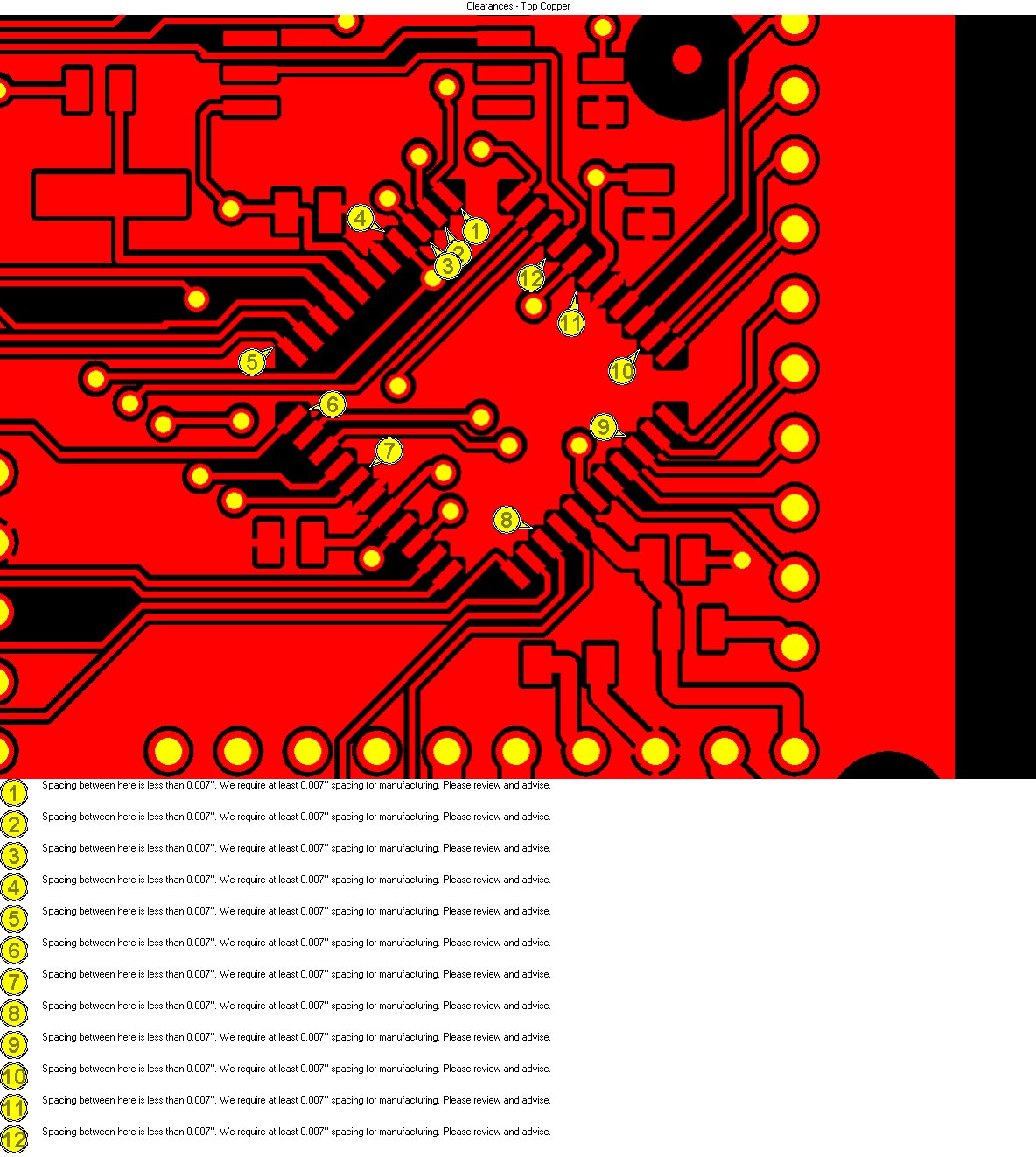

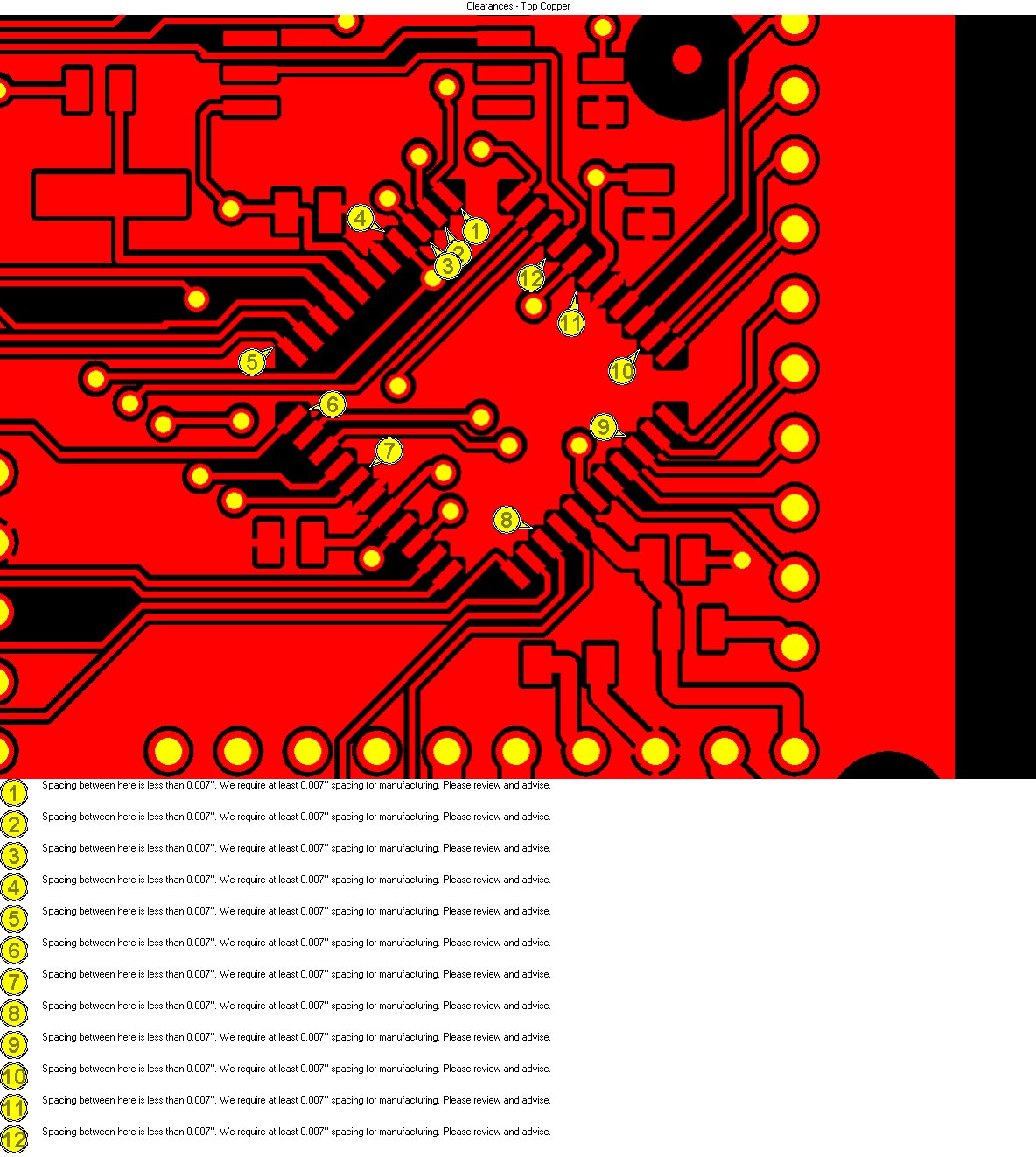

Just got a DRC fail back from APcircuits this morning.

A TQFP48 set to clearance of 8 mils (1600 clearance spec in all pads)

and placed with a rotation of 45 degrees incorrectly clears a polygon on

the pad layer. It ends up with min clearance of about 6 mils from pad

to poly.

This is at least two bugs:

1) Polygon clearance: The footprint says 1600, but the pad does not

clear that much Cu.

2) DRC: Min clearance rule is 8 mil, but this design passes DRC with

clearances of 6 mils.

APCircuits DRC picture is attached.

Checking file dates, it looks like this version of PCB was built from

CVS last December. I thought it was fresher than that... guess it's

time to rebuild anyway.

In any case, as a work-around I hand-hacked the .pcb file by enlarging

the clearance spec to 2400 on all the pads for my tqfp and shot off some

new gerbers, so hopefully the board will go through now.

-dave

_______________________________________________

geda-user mailing list

geda-user@xxxxxxxxxxxxxx

http://www.seul.org/cgi-bin/mailman/listinfo/geda-user